Even though you may or may not have heard of ARM, it is everywhere, in almost 70% of machines and 99% of smartphones. From your tab, Google Home to electric cars, ARM chipsets dominate the processor segment. But you don’t hear about them anywhere, as most chips that you hear of are made off of traditional (x86) architecture, such as your pc or laptop processors consisting of Intel or AMD chips.

So, what is ARM?

ARM or Advanced RISC Machine is a chip company founded in 1990 that designs the chips that we are talking about, named after the company ARM chips. ARM chips are different from traditional x86 architecture in their computing method. The R in ARM stands for RISC, which by itself stands for Reduced Instruction Set Computer. Traditional x86 architecture uses a different set of computing, which is more complex and is named as such, CISC or Complex Instruction Set Computer. The main difference between RISC and CISC is that RISC uses a simple set of instructions and CISC uses a complex one.

But how is simple “SIMPLE” and complex “COMPLEX”? To understand this, we have to think about what a processor does, which is giving instructions to the other components of the machine to do their job and report back to it to make sure it is done. ARM chips’ RISC employs simpler, more snappy instructions. Which is also pipelined, meaning each instruction is given at one time, and after getting it done, another instruction is given. And this loop goes on till the whole workload is done. Traditional x86 chipsets use CISC where it will give instructions all at once, and the rest of the components have to figure it out by themselves to complete the instructions set. Because of this method, there is no pipelining of instructions. Hence, it takes more time to complete the set.

But let’s say, you’re not satisfied with these simple explanations. Let’s dig deeper into ARM architecture, and understand what makes an ARM chip.

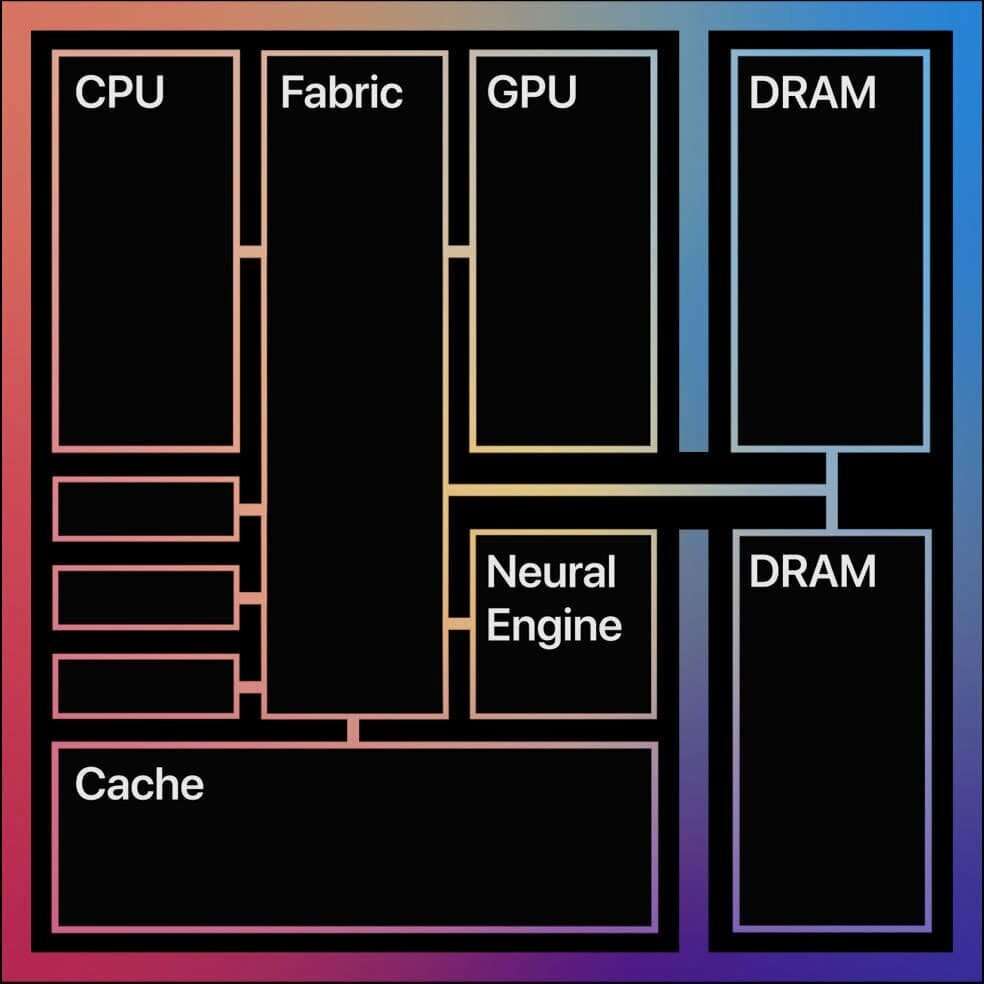

The ARM architecture provides a flexible foundation for designing chips, enabling a wide range of devices from smartphones to supercomputers. While the specific implementation details can vary between chip manufacturers, the core structure typically includes the following components:

1. Processor Core

- CPU Design: The central processing unit (CPU) is the heart of the chip, responsible for executing instructions. ARM’s RISC architecture allows for simpler, more efficient instruction sets, leading to lower power consumption and higher performance.

- Core Count: Modern ARM chips often feature multiple cores to handle complex tasks simultaneously. For example, Apple’s A-series chips used in iPhones and iPads can have up to 6 high-performance cores and 5 efficiency cores.

- Core Types: ARM chips can include different types of cores, such as:

- Performance cores: Optimized for high-performance tasks like gaming and demanding applications.

- Efficiency cores: Designed for low-power, general-purpose tasks, such as background processes and low-intensity workloads.

- Specialized cores: Tailored for specific tasks like graphics processing, machine learning, or neural network computations.

2. Cache Memory

- Levels: ARM chips typically include multiple levels of cache memory to improve performance:

- L1 cache: Small, fast cache memory integrated directly into the processor core.

- L2 cache: Larger than L1, but slower, often shared between multiple cores.

- L3 cache: Even larger and slower, shared by all cores on the chip.

- Size and Associativity: The size and associativity of each cache level affect its performance. For example, a larger cache can store more data, while higher associativity allows for more flexible data placement.

3. Memory Controller

- Memory Interface: The memory controller manages communication between the processor core and the main memory. It typically supports various memory standards, such as DDR4 and LPDDR5.

- Memory Bandwidth: The memory controller’s design affects the memory bandwidth, which is the rate at which data can be transferred between the processor and memory. Higher memory bandwidth is crucial for performance-intensive applications.

- Memory Management: The memory controller also handles memory management tasks, such as virtual memory, memory protection, and cache coherency.

4. Graphics Processing Unit (GPU)

- Integration: Many ARM chips include integrated GPUs for handling graphics-intensive tasks. These GPUs can be designed to work in conjunction with the CPU, providing efficient graphics processing capabilities.

- Performance: GPU performance varies widely depending on the chip’s target market and application. High-end mobile GPUs can offer impressive graphics capabilities for gaming and other demanding tasks.

- Features: Modern GPUs often include features like ray tracing, tensor cores for machine learning, and variable rate shading for optimizing performance.

5. Other Peripherals

- I/O Interfaces: ARM chips typically include various I/O interfaces (Input/Output) for communication with other devices, such as:

- Universal Asynchronous Receiver/Transmitter (UART): For serial communication with other devices.

- Inter-Integrated Circuit (IIC): For communication with other chips on a single board.

- Serial Peripheral Interface (SPI): For communication with simple devices like sensors and displays.

- Timers and Counters: These components are essential for timing events and controlling peripheral devices.

- Security Features: Many modern ARM chips include security features like hardware-based trusted execution environments (TEEs) to protect sensitive data.

The specific arrangement and configuration of these components can vary depending on the chip’s intended use and performance requirements. However, the underlying ARM architecture provides a common framework for designing and building these chips, enabling a wide range of applications and devices.

Why are ARM chipsets so power efficient?

| Feature | ARM | x86 |

| Instruction Set | RISC | CISC |

| Instruction Complexity | Simple | Complex |

| Clock Cycles per Instruction | Typically 1 | Can vary, often multiple |

| Power Consumption | Lower | Higher |

| Typical Applications | Mobile devices, IoT | Desktops, servers, high-performance computing |

Let’s talk about how ARM’s architecture is optimized for low power consumption through a combination of hardware and software techniques. Leaning into more power efficiency and competing with the traditional x86 chips.

Hardware-Level Optimizations:

- Transistor Size: Modern ARM chipsets often use transistors as small as 5nm or even smaller. The latest technology consists of 3nm transistors. This reduction in transistor size significantly reduces the amount of power required to switch them on and off. For instance, a 5nm transistor might consume only a fraction of the power of a 14nm transistor.

- Specialized Cores: ARM can incorporate specialized cores for specific tasks, such as graphics processing or machine learning. These cores can be designed with specific power-saving techniques tailored to their functions. For example, a graphics processing unit (GPU) might use a different power management strategy than a central processing unit (CPU).

- Power Gating: This technique involves selectively turning off parts of the chip that are not in use. This can significantly reduce power consumption, especially during periods of low activity.

Software-Level Optimizations:

- Dynamic Voltage Scaling (DVS): DVS allows the chipset to adjust its operating voltage based on the workload. This means that during periods of low activity, the voltage can be reduced, leading to significant power savings. For example, a smartphone might reduce its CPU voltage while playing a simple game compared to running a demanding 3D graphics application.

- Frequency Scaling: Similar to DVS, frequency scaling allows the chipset to adjust its clock speed based on the workload. Lower clock speeds can reduce power consumption but at the cost of performance. ARM chipsets often use a combination of DVS and frequency scaling to optimize power consumption while maintaining acceptable performance levels.

Let’s talk about some Examples:

- Apple’s A-series chips: These high-performance ARM-based processors used in iPhones and iPads have achieved impressive power efficiency through a combination of hardware and software optimizations. For example, the A16 Bionic chip, used in the iPhone 14 Pro and Pro Max, is claimed to be up to 40% more power-efficient than its predecessor A15 Bionic chip.

- Qualcomm’s Snapdragon chips: Almost every Android device on this planet uses a Qualcomm Snapdragon chipset for its processor. Qualcomm has proven itself to be the best in the market to be used in this segment. They have focused on improving power efficiency through features like Dynamic Voltage Frequency Scaling (DVFS) and heterogeneous computing, which involves using specialized cores for different tasks. Recently, they have expanded to the SnapDragon X Elite chips, using the ARM technology and it is said to be more power efficient than a Macbook 2024.

With the RISC, pipelining and the combination of hardware optimization and software optimization have led ARM chips in front of the processor race, as energy efficiency is the new currency of trade. Soon enough, there might be only ARM-based chips in the market, leaving x86 as the predecessors. ARM is the future of computing and power efficiency.